Sònrachadh

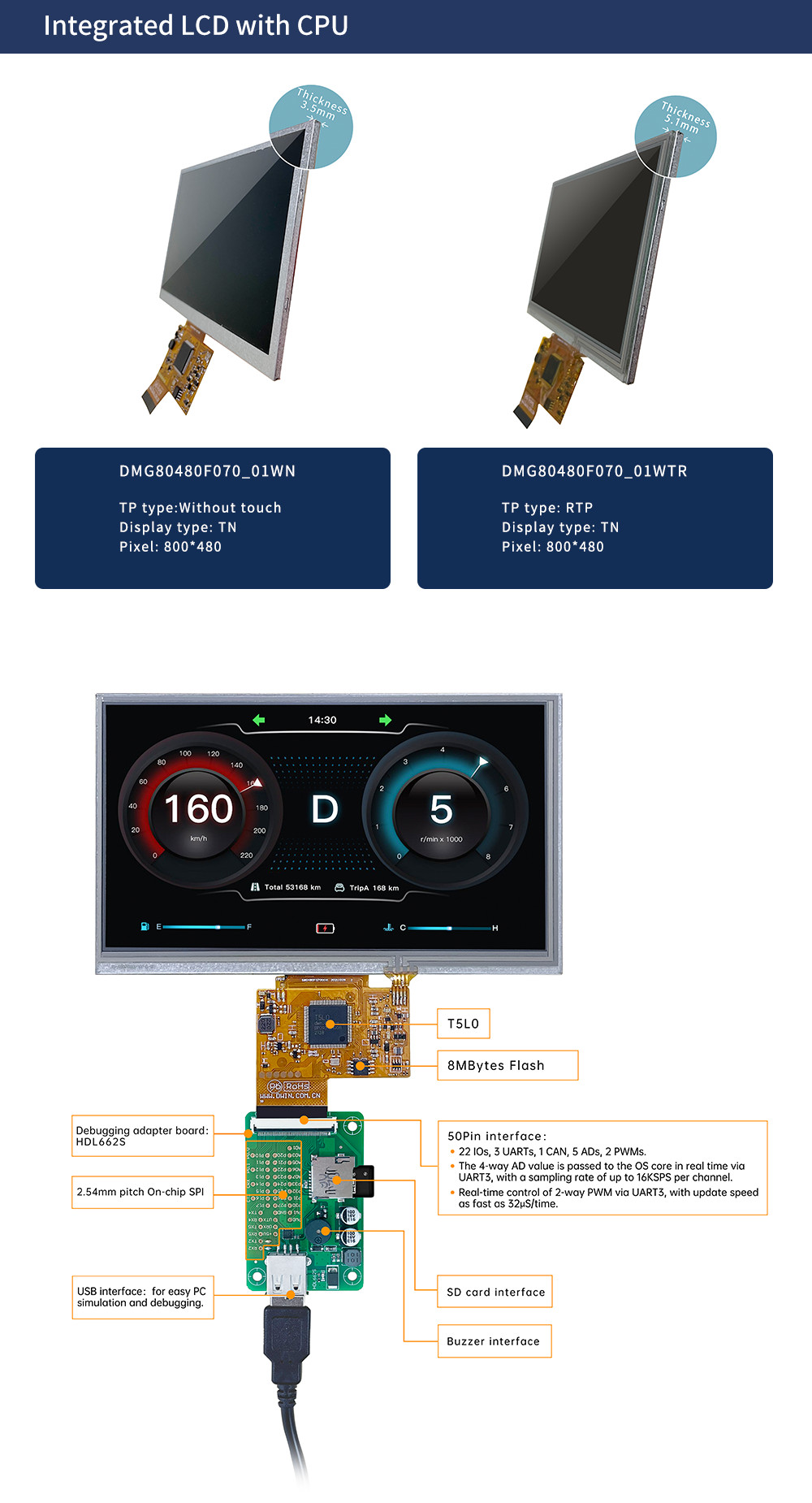

| T5L0 ASIC | Air a leasachadh le DWIN. Mòr-chinneasachadh ann an 2020,1MBytes No Flash air a’ chip, àite stòraidh caochlaideach 128Kbytes airson dàta iomlaid le OS CPU Core agus cuimhne. Ath-sgrìobh cearcall: còrr air 100,000 uair | ||

| Dath | 262K dathan | ||

| Seòrsa LCD | TN, TFT LCD | ||

| A' coimhead Ceàrn | Ceàrn seallaidh àbhaisteach, luach àbhaisteach 70 ° / 70 ° / 30 ° / 40 ° (L / R / U / D) | ||

| Raon Taisbeanaidh (AA) | 154.08mm (W) × 85.92mm (H) | ||

| Fuasgladh | 800 × 480 | ||

| Cùl-sholais | LED | ||

| Gile | DMG80480F070_01WN: 250nit | ||

| DMG80480F070_01WTR: 200nit | |||

| Seòrsa | RTP (pannal suathaidh an-aghaidh) | ||

| Structar | AM film + SEO glainne | ||

| Modh suathaidh | Cuir taic ri suathadh is slaod puing | ||

| Cruaidh uachdar | 3h | ||

| Tionndadh aotrom | Còrr is 80% | ||

| Beatha |

Dotting > 1,000,000 uair; Stròc > 100,000 uair; 150g feachd, cùl agus a mach air a mheas dà uair | ||

| Voltage cumhachd | 3.6 ~ 5.5V | ||

| Obrachadh an-dràsta | VCC = +5V, Cùl-sholais air, 410mA | ||

| VCC = +5V, Backlight dheth, 115mA | |||

| Teòthachd Obrach | -10 ℃ ~ 60 ℃ | ||

| Teòthachd stòraidh | -20 ℃ ~ 70 ℃ | ||

| Taiseachd obrach | 10% ~ 90% RH, luach àbhaisteach 60% RH | ||

| Baudrate | 3150~3225600bps | ||

| Toradh Voltage | Toradh 1, Iout = 8mA; 3.0 ~ 3.3V | ||

| Toradh 0, Iout = -8mA; 0~0.3V | |||

| Voltage a-steach(RXD) | Cuir a-steach 1;3.3V | ||

| Cuir a-steach 0;0~0.5V | |||

| Eadar-aghaidh | UART2: TTL; | ||

| UART4: TTL;( Ri fhaighinn a-mhàin às deidh rèiteachadh an OS) | |||

| UART5: TTL; (Ri fhaighinn às deidh rèiteachadh an OS a-mhàin | |||

| Cruth dàta | UART2: N81; | ||

| UART4: N81/E81/O81/N82; 4 modhan (rèiteachadh OS) | |||

| UART5: N81/E81/O81/N82; 4 modhan (rèiteachadh OS) | |||

| Socaid | 50Pin_0.5mm FPC | ||

| Flash | 8M Bytes | ||

| PIN | Mìneachadh | Tha mi/o | Tuairisgeul gnìomh |

| 1 | +5V | mi | Solar cumhachd, DC3.6-5.5V |

| 2 | +5V | mi | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | mi |

5 ADC a-steach. Fuasgladh 12-bit ann an cùis solar cumhachd 3.3V. Cuir a-steach 0-3.3V bholtaids. Ach a-mhàin AD6, thèid an còrr dàta a chuir gu OS core tro UART3 a-steach fìor-ùine le ìre samplachaidh 16KHz. Faodar AD1 agus AD5 a chleachdadh ann an co-shìnte, agus faodar AD3 agus AD7 a chleachdadh ann an co-shìnte, a tha co-ionann ri dhà 32KHz samplachadh AD. Faodar AD1, AD3, AD5, AD7 a chleachdadh ann an co-shìnte, a tha co-ionann ri samplachadh AD 64KHz; tha an dàta air a chruinneachadh 1024 tursan agus an uairsin air a roinn le 64 gus luach 64Hz 16bit AD fhaighinn le bhith a’ dèanamh cus samplachadh. |

| 7 | AD6 | mi | |

| 8 | AD5 | mi | |

| 9 | AD3 | mi | |

| 10 | AD1 | mi | |

| 11 | +3.3 | O | Toradh 3.3V, an luchd as àirde de 150mA. |

| 12 | SPK | O |

MOSFET taobh a-muigh gus clamhan no neach-labhairt a dhràibheadh. An resistor 10K taobh a-muigh bu chòir a shlaodadh sìos chun talamh gus dèanamh cinnteach gu bheil cumhachd air adhart aig ìre ìosal. |

| 13 | SD_CD | IO |

Eadar-aghaidh SD/SDHC, Bidh an SD_CK a’ ceangal capacitor 22pF ri GND faisg air làimh eadar-aghaidh cairt SD. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | IO | |

| 16 | SD_D2 | IO | |

| 17 | SD_D1 | IO | |

| 18 | SD_D0 | IO | |

| 19 | PWM0 | O |

Toradh PWM 2 16-bit. Bu chòir an resistor 10K taobh a-muigh a shlaodadh sìos gu an talamh gus dèanamh cinnteach gu bheil cumhachd-air ìre ìosal. Faodar smachd a chumail air cridhe an OS ann an àm fìor tro UART3 |

| 20 | PWM1 | O | |

| fichead 's a h-aon | P3.3 | IO |

Ma chleachdas tu RX8130 no SD2058 I2C RTC gus ceangal ris an dà IO, bu chòir SCL a bhith ceangailte ri P3.2, agus SDA ceangailte ri P3.3 aig an aon àm le resistor 10K tarraing suas gu 3.3V. |

| fichead 's a dhà | P3.2 | IO | |

| fichead 's a trì | P3.1/EX1 | IO |

Faodar a chleachdadh mar chur-a-steach taobh a-muigh 1 aig an aon àm, agus a’ toirt taic do gach cuid ìre bholtachd ìosal no modhan brisidh iomall. |

| fichead 's a ceithir | P3.0/EX0 | IO |

Faodar a chleachdadh mar chur-a-steach taobh a-muigh 0 aig an aon àm, agus a’ toirt taic do gach cuid ìre bholtachd ìosal no modhan brisidh iomall. |

| 25 | P2.7 | IO | IO eadar-aghaidh |

| 26 | P2.6 | IO | IO eadar-aghaidh |

| 27 | P2.5 | IO | IO eadar-aghaidh |

| 28 | P2.4 | IO | IO eadar-aghaidh |

| 29 | P2.3 | IO | IO eadar-aghaidh |

| 30 | P2.2 | IO | IO eadar-aghaidh |

| 31 | P2.1 | IO | IO eadar-aghaidh |

| 32 | P2.0 | IO | IO eadar-aghaidh |

| 33 | P1.7 | IO | IO eadar-aghaidh |

| 34 | P1.6 | IO | IO eadar-aghaidh |

| 35 | P1.5 | IO | IO eadar-aghaidh |

| 36 | P1.4 | IO | IO eadar-aghaidh |

| 37 | P1.3 | IO | IO eadar-aghaidh |

| 38 | P1.2 | IO | IO eadar-aghaidh |

| 39 | P1.1 | IO | IO eadar-aghaidh |

| 40 | P1.0 | IO | IO eadar-aghaidh |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | mi | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | mi | |

| 45 | P0.0 | IO | IO eadar-aghaidh |

| 46 | P0.1 | IO | IO eadar-aghaidh |

| 47 | CAN_TX | O | CAN eadar-aghaidh |

| 48 | CAN_RX | mi | |

| 49 | UART2_TXD | O | UART2 ( port sreathach UART2 de chridhe OS) |

| 50 | UART2_RXD | mi |